Tech Stack

C++

Computer Architecture

Assembly

Systems Programming

Description

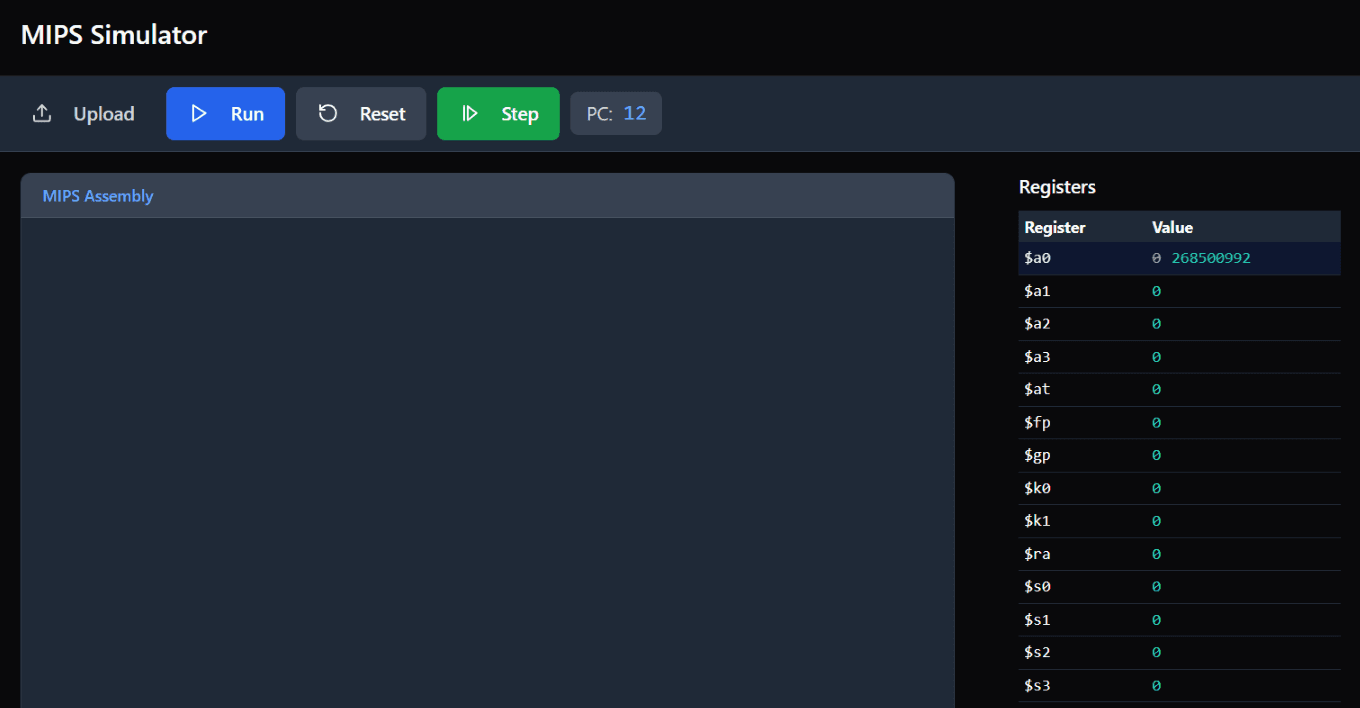

Designed and implemented a complete MIPS processor simulator with full 5-stage pipeline architecture including fetch, decode, execute, memory, and writeback stages.

Integrated advanced features including hazard detection unit, data forwarding mechanisms, and branch prediction to achieve realistic processor behavior.

Developed comprehensive debugging and visualization tools supporting 50+ MIPS instructions with detailed execution tracing and performance analysis.

- Complete 5-stage pipeline implementation with realistic timing

- Hazard detection and data forwarding for pipeline optimization

- Support for 50+ MIPS instructions including arithmetic, logical, and memory operations

- Comprehensive debugging interface with step-by-step execution

- Performance analysis tools for instruction throughput and pipeline efficiency